반도체 - 글로벌 주요 업체들의 패키지 트렌드 (22.12.20)

기존 패키지의 역할은 네가지로 나눌수 있다.

[1] 칩 보호, [2] 전기적 연결, [3] 기계적 연 결, [4] 열 방출이 있다.

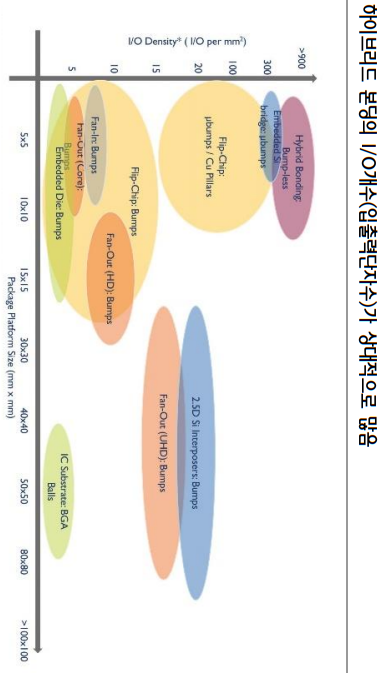

최근에는 AI(인공지능)와 자율주행 등 고성능 반도체에 대한 수요가 증가하면서 패키징 기술을 통해 반도체 속도 개선을 시도하고 있다. 패키징 기술을 통해 반 도체 성능과 생산 효율성을 높일 수 있기 때문이다.

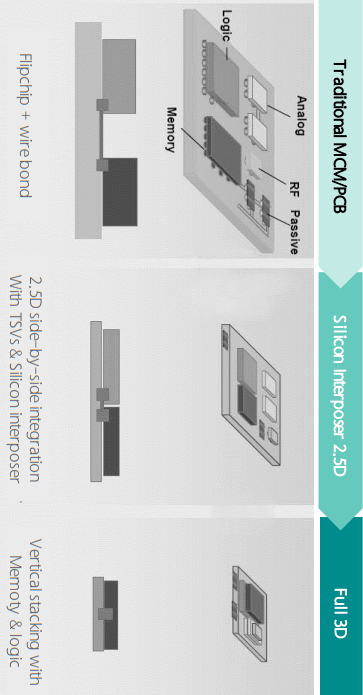

글로벌 주요 반도체 업체의 후공정 로 드맵을 살펴보면 적층 패키징을 적극적으로 채용하고 있다. 메모리 칩을 수직으로 적층하면 고속 데이터 전송이 가능해질 뿐만 아니라, 동일한 면적 내 메모리 용량을 극대화 할 수 있 기 때문이다. 또한, 메모리 반도체와 비메모리 반도체를 수직 적층해서 패키징 할 경우 비메 모리반도체가 실시간으로 처리하는 데이터를 메모리 반도체가 고속으로 저장해 많은 데이터 를 처리할 수 있다.

ㅁ 3D 적층 패키징 성장

5-1) TSMC

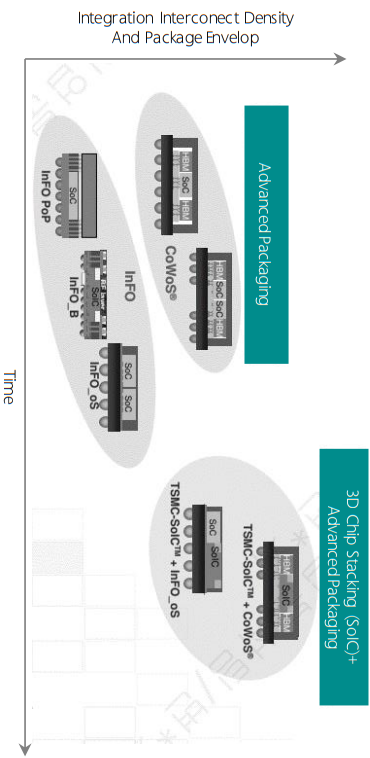

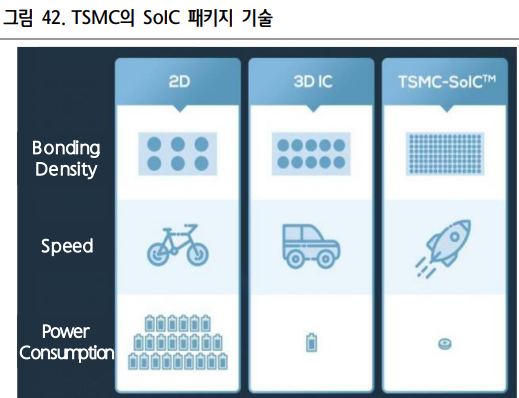

TSMC는 2022년 3월 AMD의 고성능 컴퓨팅(HPC)용 CPU를 SoIC 적층 패키지 기술로 양산했다. TSMC는 칩 사이 간격을 종전 대비 5분의 1 수준으로 줄여 전기 전도를 올리면 서 속도를 올리고 에너지 효율을 높였다. 하이브리드 패키지 기술로 고성능 슈퍼컴퓨팅 시 장의 공략 속도를 높일 예정이다.

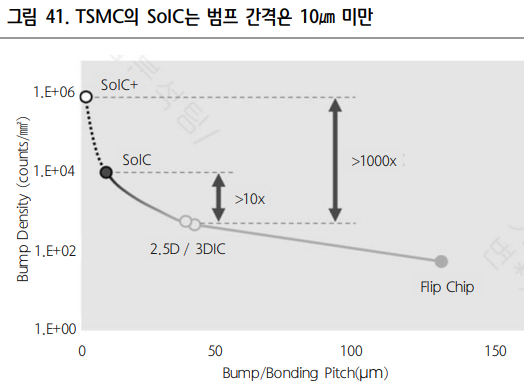

SoIC는 범프 간격이 10㎛ 미만에 불과하다. 범프 밀도가 2.5D 패키지 기술보다 10배 높고, SoIC의 두 번째 버전인 SoIC+의 경우 범프 밀도가 2.5D 패키지의 1,000배에 달한다. TSMC는 SoIC가 1㎟ 면적에 약 1만개의 상호 연결 (Interconnection)을 구현할 수 있는 기술이라고 설명한다. TSMC의 하이브리드 본딩을 사 용하는 SoIC(System on Integrated Chip) 기술을 통해 기존 3D 방식 대비 1/4로 줄어드 는 10㎛ 본딩 피치가 가능해졌다.

ㅁ TSMC의 패키지 기술 로드맵

5-2) Intel

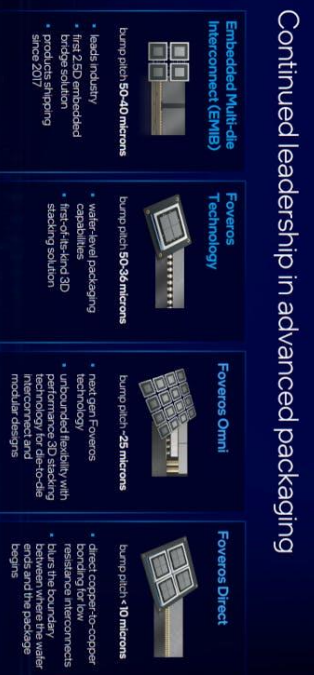

인텔은 3D 패키징 기술인 Foveros를 발표했다. 인텔의 Foveros는 하이브리드 본딩 기술로 칩 간격을 최소화한다. 반도체 여러 개를 자유롭게 연결해 데이터 처리 속도를 빠르게 하면 서도 소모 전력을 줄일 수 있다. 인텔은 2020년 출시한 Lakefield CPU에도 이 패키지 기술 을 적용했다. Intel의 EMIB 기술은 서버/데이터센터용 CPU인 Saphire Rapid 시리즈에 적 용되고, Foveros 기술은 PC용 CPU인 Meteor Lake에 적용된다. EMIB는 실리콘 브릿지를 활용한 2.5D 패키지 기술로 대면적화를, Foveros는 3D 패키지 기술로 적층의 고도화를 통 해 고다층화를 동반한다

ㅁ 인텔 Advanced Packaging 로드맵

5-3) Samsung

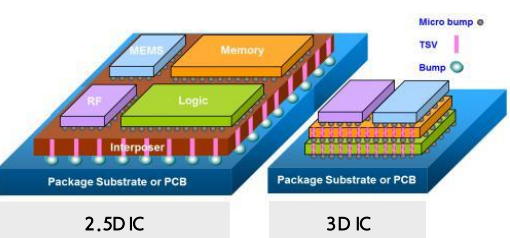

삼성전자는 2020년 3D 적층 기술 X-Cube를 공개했다. X-Cube는 로직과 SRAM을 수직으로 적층한 3D 패키지 기술이다. 3D 패키지는 구성 요소를 수직으로 쌓아 칩 공간을 절약 하며, 칩 사이의 공간을 줄임으로써 표면적을 줄이고 범핑 성능을 높인다. 대형 사이즈의 칩 을 제작할 때의 위험을 획기적으로 줄여줌으로써 높은 대역폭을 확보하고 저전력 성능을 유 지하면서도 비용은 낮아진다. 삼성전자 I-Cube는 실리콘 인터포저 위에 CPU, GPU 등의 로직과 HBM을 배치해 하나의 반도체처럼 동작하도록 하는 2.5D 패키지 기술이다. 2.5D 패키지는 병렬 수평 칩 배치를 통해 칩에서 나오는 열을 배출하고 성능을 확장한다.

ㅁ 삼성 Advanced Packaging 로드맵

5-4) 이종집적

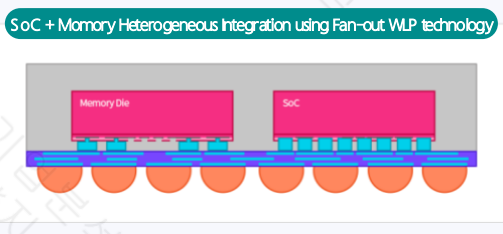

이종집적(Heterogeneous Integration)은 다른 반도체 소자들을 실리콘 인터포저(Silicon Interposer)와 TSV(Through Silicon Via) 기술들을 적용해 적층한 패키지 기술이다. 삼성 전자는 이종 집적화 패키지 기술을 적용한 '아이큐브4(I-Cube4)'를 개발했다. . I-Cube4는 2.5D 패키지 기술을 적용했다. 삼성전자가 개발한 아이큐브는 인터포저 위에 CPU, GPU 등의 로직칩과 HBM을 배치해 하나의 반도체처럼 동작하도록 하는 반도체 패키지 기술이 다. 아이큐브 뒤에 붙는 숫자는 HBM 칩의 개수를 의미한다. 인쇄회로기판(PCB) 대신 인터 포저 위에 메모리와 로직 반도체를 올렸다. 여러 개의 칩을 한 개의 패키지 안에 배치해 데 이터 전송 속도를 높이고, 패키지 면적을 줄일 수 있다. 작은 폼펙터(구조)로 다기능을 구현 할 수 있어 AI 등 다양한 분야에 광범위하게 활용할 수 있다.

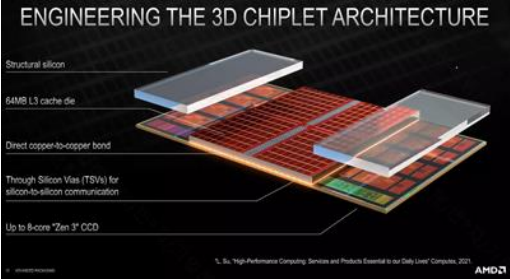

적층 패키징 구조가 관심 받는 이유는 디바이스 적층을 통해 대역 폭 증가, 소비 전력 감소, 면적 축소가 동시에 가능하기 때문이다. 3D 적층은 기존 수평 구조로 만들던 반도체 셀을 3D 수직 구조로 쌓아 올리는 방식이다. 대표적으로 AMD의 3D V-Cache 후공정 기술이 있다. V-Cache는 TSV와 하이브리드 본딩을 사용해 구현한 3D 패키지다. AMD는 이 공정 을 데이터센터용 CPU 라인업인 EPYC 제품에도 적용할 예정이다.

ㅁ Samsung 2.5D 패키지 기술을 활용한 I-Cube 4

ㅁ fan-out WLP 기술을 이용한 SOC와 메모리 이종접합

ㅁ 3D 적층 기술을 이용한 AMD 3D V-Cache

ㅁ 2.5D와 3D 적층 패키징 비교

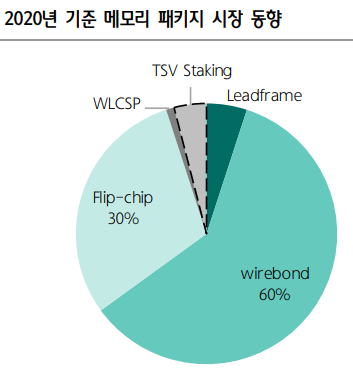

5-5) TSV

3D 패키지 발전으로 TSV 기술이 주목받고 있다. TSV는 Through Silicon Via 약자다. 반도체에 구멍(Via hole)을 뚫어 상,하단 반도체 칩을 전극으로 연결하는 방식으로, 메모리칩 을 적층하여 대용량 구현이 가능하다. TSV는 복잡한 와이어와 와이어를 연결할 공간이 필요 없어 패키지의 크기를 줄일 수 있다

TSV는 기술적, 비용적 한계로 HBM(고대역 메모리)이나 CIS(이미지센서) 패키지에 우선적 으로 적용하고 있다. SK하이닉스는 HBM 패키징으로 TSV 기술을 적용하고 있다. TSV는 고속, 고용량, 작은 크기, 저전력 요구를 만족시켜 메모리에서 TSV를 이용한 적층 기술이 적극 개발되고 있다. TSV는 기술 난도가 높고 고비용이지만 이전 장비를 이용해도 스케일다 운 효과가 있어 가격 경쟁력이 있다고 평가받고 있다.

ㅁ 주요 반도체 업체들의 HBM과 하이브리드 본딩 기술 로드맵

TSV는 I/O 개수를 늘릴 수 있다는 장점 때문에 DRAM의 새로운 아키텍처로 개발된 메모리 HBM(High Bandwidth Memory)에 사용된다. HBM은 여러개의 D램을 수직으로 연결해 기존 D램보다 데이터 처리 속도를 혁신적으로 끌어올린 고부가가치, 고성능 제품이다.

기존 DRAM은 와이어 공정상의 한계 때문에 32 비트가 한계였다. 정보를 전달할 수 있는 핀의 개수가 32개라는 것을 의미한다. 이 핀의 개수를 늘리면 더 많은 정보를 동시에 보낼 수 있다. TSV를 이용한 HBM의 경우 1,024 비트까지 구현할 수 있다. HBM에 형성될 TSV 개수는 2,000개에서 3,000개 수준이다.

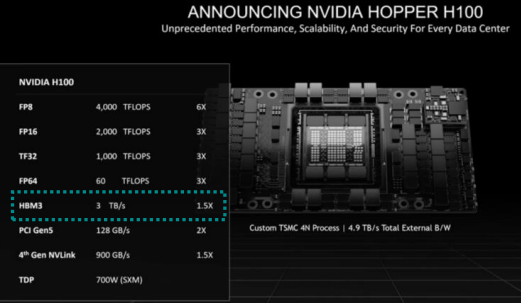

SK하이닉스는 HBM3 제품의 양산을 시작했다. 해당 제품은 기존 D램 대비 데이터 처리 속도를 크게 향상시킨 것이 특징으로, 엔비디아의 차세대 GPU H100과 결합될 예정이다. HBM3는 초당 819GB(기가바이트), FHD급 영화(5GB) 163편 분량의 데이터를 1초 만에 처리할 수 있는 수준이다.

ㅁ 엔비디아 신제품 H100에 SK하이닉스 HBM3를 결합하기로 결정

ㅁ GDDR5와 HBM3 성능 비교

5-6) 하이브리드 본딩

기존 3D 적층 패키지 기술은 본딩 간격(bonding pitch)의 한계로 성능과 대역폭을 개선하 기 어려워졌다. 본딩은 웨이퍼와 웨이퍼, 혹은 칩과 웨이퍼를 전기적으로 연결하는 기술이다. 주로 공 모양의 범프(Bump)를 그 사이에 넣는 방식을 활용한다. 범프 크기와 간격이 좁 을수록 더 많은 범프를 넣을 수 있어 대역폭 및 성능을 개선할 수 있다. 범프 간의 간격이 10㎛까지 축소되면서 하이브리드 본딩 기술이 주목받기 시작했다.

하이브리드 본딩은 범프 없이 구리 배선의 패드끼리 직접 붙이는 기술로, 전기신호 밀도를 1,000배 이상으로 올릴 수 있다. 하이브리드 본딩은 주로 HPC, 서버, 데이터센터, AI 등 하이엔드 컴퓨팅을 중심으로 적용될 예정이다.

AMD는 2022년 애널리스트데이에서 새 중앙처리장치(CPU) 설계 기반이 되는 ZEN4와 ZEN5 아키텍처를 공개했다. AMD는 하이브리드 본딩 공정을 확대 적용한다는 방침을 세우 고 있다. 하이브리드 공정은 공정 과정에서 홈이 잘 형성되었는지 계측할 수 있는 원자현미 경(AFM)과 잘라낸 다이를 다른 다이와 연결하는 하이브리드 본더 장비가 필요하다. 아울러 후공정 단계에서 하이브리드 본딩으로 갈 경우 새로운 다이싱 방식이 필요할 것으로 예상되 는데 레이저 다이싱 장비가 사용될 것으로 기대된다.