산업공부/반도체

반도체 보너스3 Low-K의 모든 것(Low-K 밸류체인, 스택VS트렌치)

시위를 벗어난 화살처럼

2023. 7. 4. 11:56

[함께배우기] 36일차, 반도체 보너스3 Low-K의 모든 것(Low-K 밸류체인, 스택VS트렌치) - YouTube

디램은 게이트에 전압을 인가하면 소스에서 드레인으로 전하가 이동해 커패시터에 이 전하들이 저장됨.

커패시터 성능은 전하의 저장량과 관계가 있음.

낸드는 커패시터가 없음. 게이트에 전압을 인가하면 Bottom 게이트에 전하가 저장됨.

스택 방식과 트렌치 방식이 경쟁을 했으나 스택 방식이 이김. (난이도가 스택 방식이 더 쉬웠기 때문)

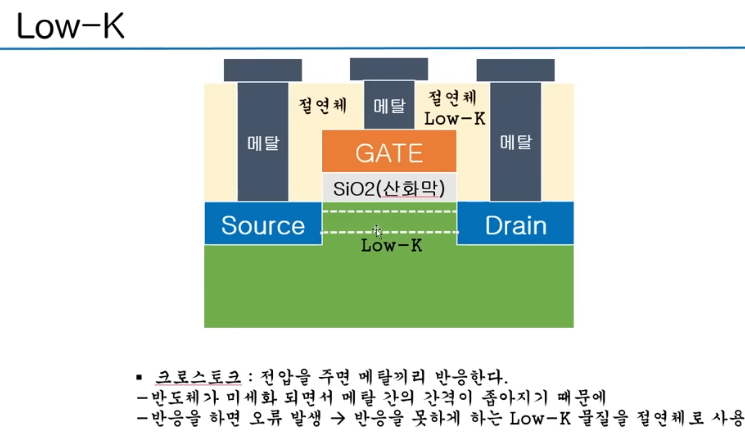

소스와 드레인 사이에는 전하가 이동해야 하는데, High-K를 사용하면 전하가 이동에 방해를 받음.

이곳에는 Low-K 소재를 사용해야 함. (Low-K 물질 증착은 CVD 방식으로 함)

Low-K 소재를 하는 회사는 일본의 아데카와, 디엔에프,

HCDS는 덕산테코피아 유명함. 낸드쪽에도 쓰임.

| 소스와 드레인 사이 채널 형성 부분에 low-K를 사용하는 이유는 커패시터와 같은 현상이 적게 일어나게 하기 위함. (공유) 반도체 공부 - 프리커서, 전구체, .. : 네이버블로그 (naver.com)  |

원래 반도체 위에는 메탈로 연결되어 있음. 왜냐하면 전하를 인가해 줘야 하니까.

그런데 각각의 메탈끼리 서로 반응하면 안됨. 미세화가 진행되면 될수록 메탈 사이의 간격은 줄어들고, 문제가 생각 가능성이 커짐. 그래서 Low-K 소재로 절연을 해줘야 함.

3D 낸드로 적층할 때 임시로 기둥을 만들어줘야 하는데 이때 Low-K 물질을 이용.

이것을 잘하는 회사가 덕산테코피아(??)

#Low-K 밸류체인

728x90